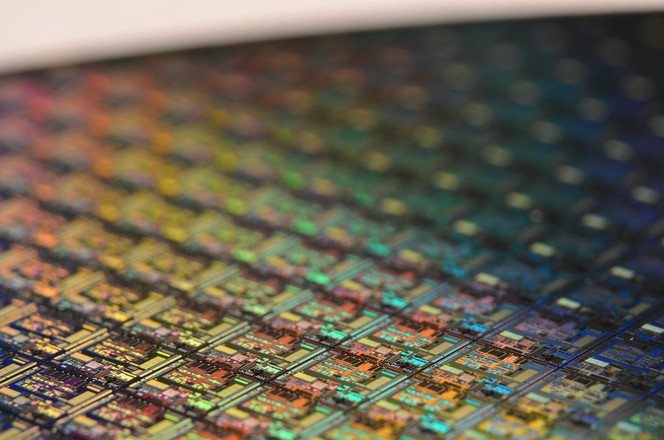

Pour répondre aux besoins des datacenters, la firme américaine Cerebras a imaginé un système de puce dotée de milliers de coeurs reliés entre eux et posés sur un wafer.

Cette conception de puce sur wafer permet de disposer d’une très grosse puissance de calcul rassemblée sur une surface réduite sans avoir à multiplier les systèmes annexes d’interface de communication, de réseau et de refroidissement.

Cette idée, la Chine est en train de la reprendre à son compte avec le développement d’une premier démonstrateur de système de multi-chiplets de 256 coeurs qui pourra donner naissance à une puce de 1600 coeurs occupant un wafer.

L’architecture RISC-V à l’honneur

Cette quête des Big Chips doit permettre de passer outre certaines limitations techniques inhérentes à la loi de Moore et assurer malgré tout la croissance des performances des systèmes informatiques.

Chiplet Zhejiang pour une future puce sur wafer

Point intéressant, le système de 256 coeurs Zhejiang exploite une gravure de 22 nm réalisée par SMIC et se compose de 16 chiplets comprenant chacun 16 coeurs avec une architecture RISC-V.

L’alternative aux architectures ARM et x86 est de plus en plus utilisée en Chine pour différents types de systèmes informatiques et elle trouve logiquement sa place dans la conception de systèmes géants pour datacenters capables d’atteindre l’échelle exascale.

La Chine sur la voie des puces sur wafer

Le site The Next Platform note que rien n’empêche de dupliquer la puce Zhejiang pour en faire un système de puce sur wafer pour créer un ensemble de milliers de puces.

Le seul frein sera alors la taille du wafer (300 mm, en attendant de futurs wafers en 450 mm) et la finesse de gravure, ainsi que la consommation d’énergie générée par un tel ensemble.

Il reste donc à avoir si une puce sur wafer finira par voir le jour en Chine mais la plupart des éléments théoriques et pratiques sont déjà explorés et pourraient donner lieu à des annonces dans les années à venir.