Le groupe AMD poursuit son offensive dans les processeurs pour serveur de belle manière avec une gamme Epyc qui gagne des parts de marché sur Intel année après année.

L’actuelle famille Epyc de 4ème génération, nom de code Genoa et Bergamo) a permis de passer aux coeurs Zen 4 et Zen 4c ainsi qu’à un nouveau socket SP5 permettant de profiter des dernières avancées en matière de mémoire et d’interface de communication.

La prochaine génération conduit aux processeurs Epyc de 5ème génération portant le nom de code Turin et dont les informations sur les caractéristiques sont encore minces.

Visite de Turin en photos

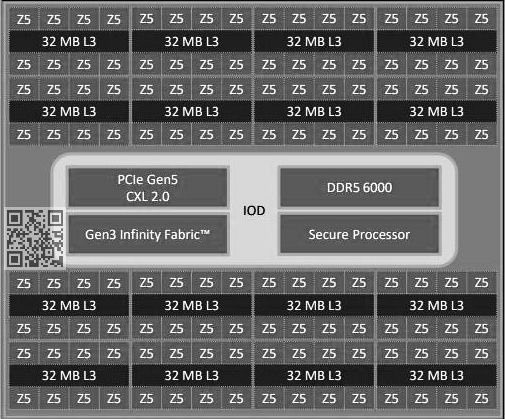

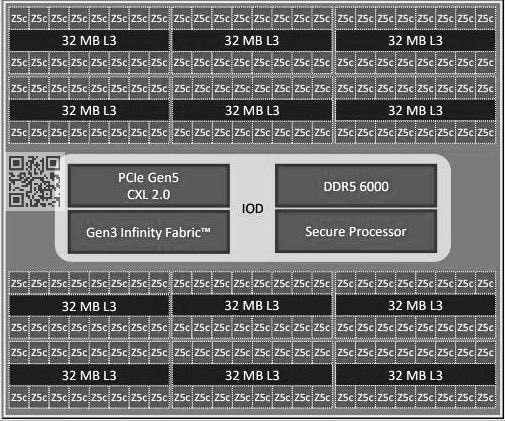

On sait tout de même que ces processeurs exploiteront l’architecture de coeur AMD Zen 5 et sa variante Zen 5c allégée. Cela donnerait deux versions : Turing Dense allant jusqu’à 192 coeurs Zen 5c et Turing Classic grimpant jusqu’à 128 coeurs Zen 5, toujours avec le socket SP5 et le support de la RAM DDR5-6000 (au lieu de 4800 à 5600).

AMD Epyc Turin Classic en Zen 5

AMD Epyc Turin Dense en Zen 5c

Pour la première fois, le leaker Yuuki_AnS en dévoile des images et les diagrammes montrant la disposition des coeurs, de la mémoire et des interface. Turing Classic regroupera ses coeurs en 16 CCD tandis Turing Dense intègrera 12 CCD, chaque groupe disposant de 32 Mo de cache L3, soit un total de 512 Mo.

Après Turin, une prochaine destination : Venice

D’autres sources en apprennent un peu plus sur la génération suivante, Venice (Epyc de 6ème génération) qui devrait proposer une variante Venice Classic avec coeurs Zen 6 et socket SP8 et une version Venice Classic avec coeurs Zen 6 et socket SP7. Les deux plates-formes devraient pouvoir gérer de la DDR5 encore plus rapide et une interface PCIe Gen 6.

On devrait entendre parler de l’architecture Zen 5 en 2024 et il reste à voir quel timing AMD donnera pour le lancement des prochains processeurs Epyc pour serveurs, sachant que la firme avait laissé filer deux ans entre les deux générations précédentes.